Information: Starting test design rule checking. In this design, there are two clocks and I want to add 6 scan chains in it. Also: always use always_ff or always_comb, never use always.Bit fifo_lvl ,fifo_lvl2 bit valid, en //Collect the value fifo_lvl, when valid is high //when en = & after one clk cycle of Compare with fifo_lvl = fifo_lvl2. ADLSoft MultiClock está dentro de Ferramentas de Escritório, na subcategoria Marcação de tempo. I have created a simple multi clock example according to lab4 model composer tutorial with a source subsystem containing gateway in blocks and a added and a sink subsystem containing gateway out block and a display. Hi, I am trying to use DFT compiler to insert scan chain to the design, but there are some errors, and I can not find out the reason. This must also be added to your property. The reset can be synchronous or asynchronous as you choose. That is, both x and temp should have resets local to their individual clock domains. The flipflops created should have resets.

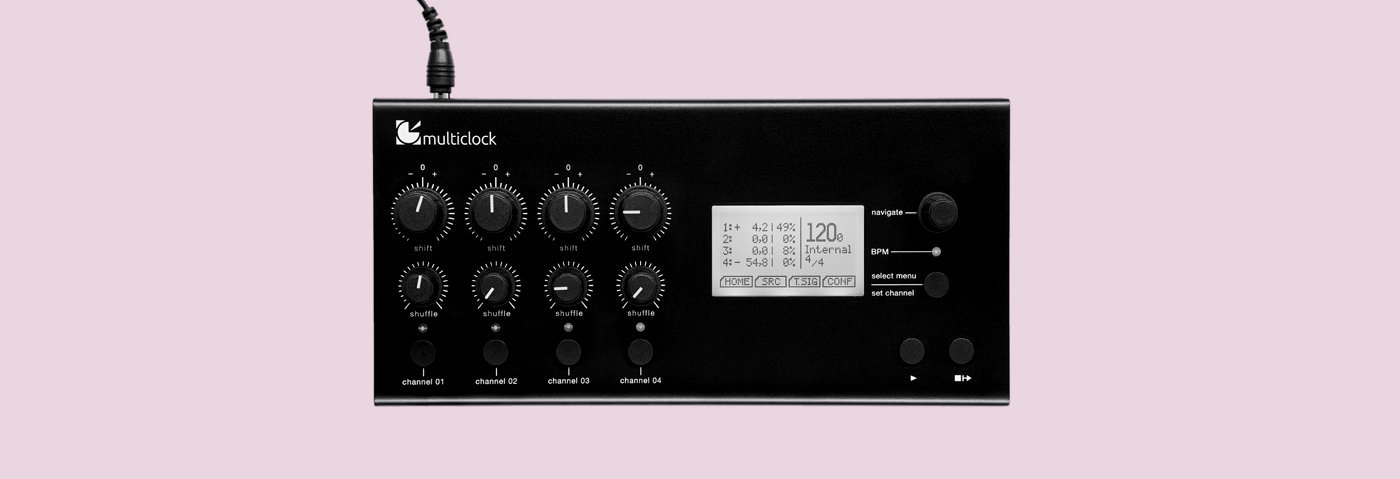

ADLSOFT MULTICLOCK UPDATE

If the above doesn't work, or if it seems like a waste to start parallel assertions checking the same thing, the following code might work.Įdit2: Put x inside property and changed two final lines in property to update x to correct values. Thus you cannot check the value made by some other instance of this assertion. Changing BPM in Ableton, changes the BPM on the Multiclock - OK 4.

ADLSOFT MULTICLOCK HOW TO

This comes at the expense of the Silent Way learning curve. How To Sync Your DAW With Any Synthesizer Using ERM Multiclock - YouTube 0:00 / 15:10 Intro ERMMulticlock midisync How To Sync Your DAW With Any Synthesizer Using ERM Multiclock Mayen Music.

ADLSOFT MULTICLOCK SOFTWARE

This means you can software monitor or hardware monitor, or a mix of both types of monitoring at the same time. E-RM receives the audio signal and sets the clock - OK 3. It allows for clock offsets that are independent of MIDI note timing, and you can place both clock & notes pretty much at any point in time, to the sample. It contains well written, well thought and well explained computer science and programming articles, quizzes and practice/competitive programming/company interview Questions. E-RM plugin is setup on a standard Midi Track sending an audio signal out from RME output 6 to Multiclock audio in - OK 2. I removed the out = x ^ x check from line #3 because x is local to the property. Just using one synth (Sub37) to start simple. Thus t will be updated to the new value on every posedge of clkA and you will have n assertions checking the same thing(which isn't a problem). Each channel can be set to either emit MIDI, DIN sync or analogue clock. A possible fix might be to declare the variable t outside the property scope. I must admit that I am hazy on the scoping of values local to a property, but check if this is causing you troubles. Lastly, what happens if clkA is much faster than clkB? Several assertions will start in parallel and disagree on the actual value of t on the first posedge of clkB. Multiclocked sequences are built by concatenating singly clocked subsequences using the single-delay concatenation operator 1 or the zero-delay concatenation operator 0.

In that case the following would be more correct, although the previous code might still work. sv1800'2017 16.13.1 Multiclocked sequences. The way I read this the assertion should start on every clkA, and then a sequence will always follow. Line #2 is not e prerequisite for line #3, and the same can be said for line #3 and line #4. In my experience a non-overlapping implication will cause the assertion to sample not on the next clkB, but skip one clkB and then sample on clkB.įurthermore I don't quite understand why you are using implications all the way through your assertion. That is, with a overlapping implication in the clock handover.

0 kommentar(er)

0 kommentar(er)